Gambar 194 memperlihatkan perbandingan antara JFET dengan BJT

Dibawah ini merupakan tabel yang membandingkan antara JFET dengan BJT

2 Konstruksi dan karakteristik Transistor JFET

transistor JFET (UJT) memiliki dua tipe yaitu Channel n dan Channel p. Konstruksi Transistor JFET Channel n merupakan persambungan tiga susunan lapisan bahan semikonduktor yaitu bahan p, bahan n, dan bahan p sedangkan Channel p merupakan persambungan tiga susunan lapisan bahan semikonduktor yaitu bahan n, bahan p, dan bahan n seperti gambar 195.

a) Karakteristik JFET Channel n adalah seperti gambar 196, dimana semakin kecil nilai VGS terhadap nol maka semakin kecil elektron mengalir dari kaki Source (S) ke kaki Drain (D) karena dari konstruksinya terlihat daerah depletion layer antara bahan semikonduksi tipe n dengan tipe p semakin membesar.

Pada kurva karakteristik output dibagi tiga operasi yaitu:

1. daerah saturasi (saturation region) yaitu daerah diatas VGS = 0 V yang artinya output menjadi cacat,

2. daerah aktif (active ragion) yang artinya output tidak cacat asalkan tegangan VGSberfluktuasi lebih kecil atau sama dengan 0 V.

3. Daerah cutoff yang artinya output akan terpotong (cacat) jika VGS lebih kecil dari VP.

4. Sedangkan tegangan VDS lebih kecil dari + VP maka JFET bersifat sebagai resistansi.

b) Karakteristik JFET Channel p adalah seperti gambar 197, dimana semakin besar nilai VGS terhadap nol maka semakin kecil hole mengalir dari kaki Source (S) ke kaki Drain (D) karena dari konstruksinya terlihat daerah depletion layer antara bahan semikonduksi tipe n dengan tipe p semakin membesar.

Pada kurva karakteristik output dibagi tiga operasi yaitu:

1.daerah saturasi (saturation region) yaitu daerah diatas VGS = 0 V yang artinya output menjadi cacat,

2.daerah aktif (active ragion) yang artinya output tidak cacat asalkan tegangan VGS berfluktuasi lebih besar atau sama dengan 0 V.

3.Daerah cutoff yang artinya output akan terpotong (cacat) jika VGS lebih besar dari VP.

4.Sedangkan tegangan VDS lebih kecil dari + VP maka JFET bersifat sebagai resistansi.

Ada 3 macam rangkaian pemberian bias, yaitu:

1. Fixed bias yaitu, arus bias IG didapat dari VGG yang dihubungkan ke kaki G melewati tahanan RG seperti gambar 198.

2. Self Bias adalah arus input didapatkan dari pemberian tegangan input VBB seperti gambar 199.

3. Voltage-divider Bias adalah tegangan VG didapatkan dari tegangan di R2 dari hubungan VDD seri dengan R1 dan R2 seperti gambar 200.

4 Konfigurasi-konfigurasi penguat satu tingkat dan rangkaian ekivalen hybrid л

Adapun rangkaian CS Amp. adalah seperti pada gambar 203.

a). rangkaian ekivalen hybrid л CS Amp. pada frekuensi menengah adalah seperti pada gambar 204.

b). rangkaian ekivalen hybrid л CS Amp. pada frekuensi rendah adalah seperti pada gambar 205.

hc). rangkaian ekivalen hybrid л CS Amp. pada frekuensi tinggi adalah seperti pada gambar 206.

Adapun rangkaian CD Amp. adalah seperti pada gambar 207.

Analisa rangkaian hybrid лnya adalah sebagai berikut.

a). rangkaian ekivalen hybrid л CD Amp. pada frekuensi menengah adalah seperti pada gambar 208.

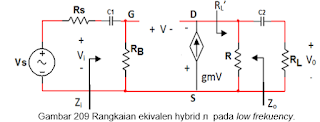

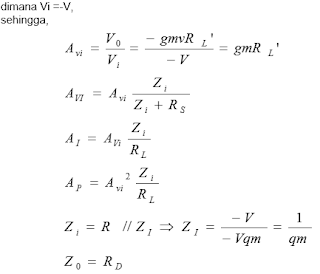

b). rangkaian ekivalen hybrid л CD Amp. pada frekuensi rendah adalah seperti pada gambar 209.

n 4.3 Common Gate (CG) Amp.[kembali]

Adapun rangkaian CG Amp. adalah seperti pada gambar 211.

Analisa rangkaian hybrid л-nya adalah sebagai berikut.

a). rangkaian ekivalen hybrid л CG Amp. pada frekuensi menengah adalah seperti pada gambar 212.

b). rangkaian ekivalen hybrid л CG Amp. pada frekuensi rendah adalah seperti pada gambar 213.

c). rangkaian ekivalen hybrid л CG Amp. pada frekuensi tinggi adalah seperti pada gambar 214.

Berikut contoh rangkaian dan hasil simulasi rangkaian bertingkat CS-CS Amp seperti gambar 215.

Adapun hasil simulasi rangkaian bertingkat CS-CS Amp. adalah seperti gambar 216.

Tidak ada komentar:

Posting Komentar